- 您现在的位置:买卖IC网 > Sheet目录335 > IX2R11S3T/R (IXYS)IC DRVR HALF BRIDGE 2A 16-SOIC

IX2R11

U1

HS

IX2R11

VCH

HGO

+ C2

10uF

C5

0.1uF

HGO

OUTPUT MONITOR

VDD

HS

GND2

GND2

HS

HV SCOPE PROBE

HIN

ENB

LIN

DG

LS

LS

VCL

LGO

LS

C6

0.1uF

L1

200uH

+ C3

10uF

D1

+

C1

100uF/250V

V1

1

18V

U2

Vin

78L15

Vout

15V

3

GND1

dVs/dt > 50V/ns

BATTERY

2

GND1

HV

600V

15V

V3

C8

C9

10uF

Measure dV/dt (HV Scope Probe)

PULSE

BNC

GND2

U3

2

3

HCPL-314J

?

14

VEE

VCC

16

OUT

15

10K

2

U2

1,8

IXDD414

4,5

6,7

0.1uF

Q1

IXFP4N100Q

D2

DSEI12-10A

GND3

-600V

GND3

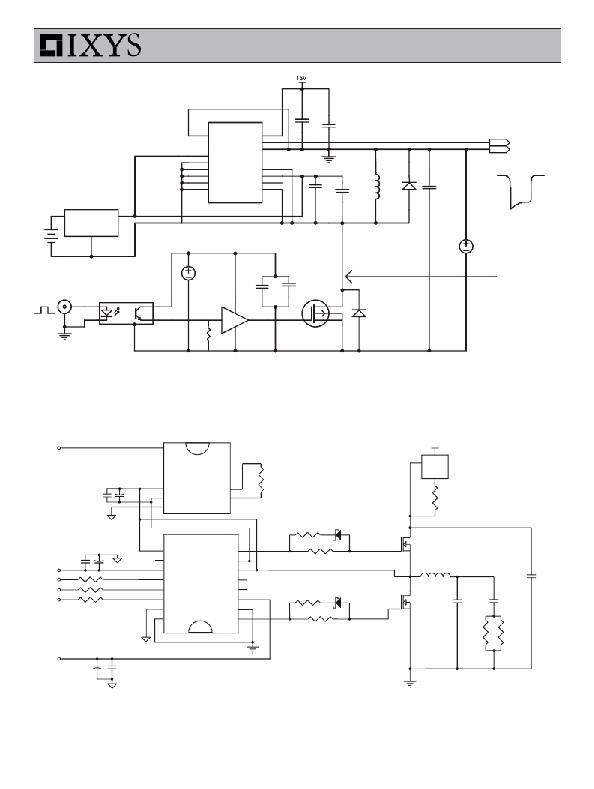

Figure 9. Test circuit for allowable offset supply voltage transient.

V CH

1

VIN+

Up to 400V

3

1

IXCP

10M90S

10

VOUT-

VOUT- 15

1k

2

1uF/35V MLCC

11

12

VOUT+

GND

VOUT+ 14

30

5.1

1N5817

1uF/35V MLCC

11

HS

HGO

8

15

IXTH14N60P

12

NC

V CH

7

V DD

HIN

ENB

1k

1k

10uF/35V

13

14

15

V DD

HIN

ENB

HS

NC

NC

6

5

4

18uH

0.1uF/1kV

LIN

1k

16

LIN

V CL

3

5.1

1N5817

0.47uF

0.47uF

17

18

DG

LS

LS

LGO

2

1

15

IXTH14N60P

V CL

10uF/35V

1uF/35V MLCC

Figure 10. Test circuit for high frequency, 750kHz, operation.

V DD , V CH , V CL = 15V

IXYS reserves the right to change limits, test conditions, and dimensions.

6

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

IX4R11S3T/R

IC DRVR HALF BRIDGE 4A 16-SOIC

IX6R11S6T/R

IC DRVR HALF BRIDGE 4A 18-SOIC

IXA531S10T/R

IC BRIDGE DRVR 3PH 500MA 48-MLP

IXA611S3T/R

IC DRIVER HALF BRDG 600MA 16-SOI

IXBD4410PI

IC LOW SIDE DRIVER 16DIP

IXD611S7T/R

IC DRVR HALF BRIDGE 600MA 14SOIC

IXDD404SIA-16

IC MOSFET DRVR DUAL 4A 16-SOIC

IXDD408YI

IC MOSFET DRVR LS 8A SGL 5TO-263

相关代理商/技术参数

IX-30-0001

功能描述:脉冲变压器 IX5 Pulse transform THT 1A RoHS:否 制造商:Murata Power Solutions 安装风格:SMD/SMT 匝数比:1:1:1 电感:1890 uH 次级线圈电阻: 电压时间 - Et: 长度:12.7 mm 宽度:9.52 mm 高度:6.35 mm

IX3120

制造商:CLARE 制造商全称:Clare, Inc. 功能描述:2.5A Output Current Gate Driver Optocoupler

IX3120G

制造商:IXYS Integrated Circuits Division 功能描述:OptoCoupler 1-CH 8-Pin PDIP Tube 制造商:IXYS INTEGRATED CIRCUITS DIVISION 功能描述:IC GATE DRIVER OPTOCOUPLE 8DIP

IX3120GS

制造商:IXYS Integrated Circuits Division 功能描述:OptoCoupler 1-CH 8-Pin PDIP SMD Tube 制造商:IXYS INTEGRATED CIRCUITS DIVISION 功能描述:IC GATE DRIVER OPTOCOUPLE 8SMD

IX3120GSTR

制造商:IXYS Integrated Circuits Division 功能描述:OptoCoupler 1-CH 8-Pin PDIP SMD T/R

IX3180G

功能描述:2.5A Gate Driver Optical Coupling 3750Vrms 1 Channel 8-DIP 制造商:ixys integrated circuits division 系列:- 包装:管件 零件状态:有效 技术:光学耦合 通道数:1 电压 - 隔离:3750Vrms 共模瞬态抗扰度(最小值):10kV/μs 传播延迟 tpLH / tpHL(最大值):200ns,200ns 脉宽失真(最大):65ns 上升/下降时间(典型值):25ns,25ns 电流 - 输出高,低:2A,2A 电流 - 峰值输出:2.5A 电压 - 正向(Vf)(典型值):1.35V 电流 - DC 正向(If):20mA 电压 - 电源:10 V ~ 20 V 工作温度:-40°C ~ 100°C 安装类型:通孔 封装/外壳:8-DIP(0.300",7.62mm) 供应商器件封装:8-DIP 认可:UR 标准包装:50

IX3180GS

功能描述:2.5A Gate Driver Optical Coupling 3750Vrms 1 Channel 8-SMD 制造商:ixys integrated circuits division 系列:- 包装:管件 零件状态:有效 技术:光学耦合 通道数:1 电压 - 隔离:3750Vrms 共模瞬态抗扰度(最小值):10kV/μs 传播延迟 tpLH / tpHL(最大值):200ns,200ns 脉宽失真(最大):65ns 上升/下降时间(典型值):25ns,25ns 电流 - 输出高,低:2A,2A 电流 - 峰值输出:2.5A 电压 - 正向(Vf)(典型值):1.35V 电流 - DC 正向(If):20mA 电压 - 电源:10 V ~ 20 V 工作温度:-40°C ~ 100°C 安装类型:表面贴装 封装/外壳:8-SMD,鸥翼型 供应商器件封装:8-SMD 认可:UR 标准包装:50

IX-3H1DC12

制造商:PolyPhaser 功能描述:EMP/LIGHTNING PROTECTOR